Einführung

Das Ziel des MOSFET besteht darin die Gate-Source-Spannung UGS anzuheben und so den MOSFET zu öffnen, sprich die Drain-Source-Spannung (UDS) auf nahezu 0V zu bekommen.

UGS steigt -> UDS sinkt

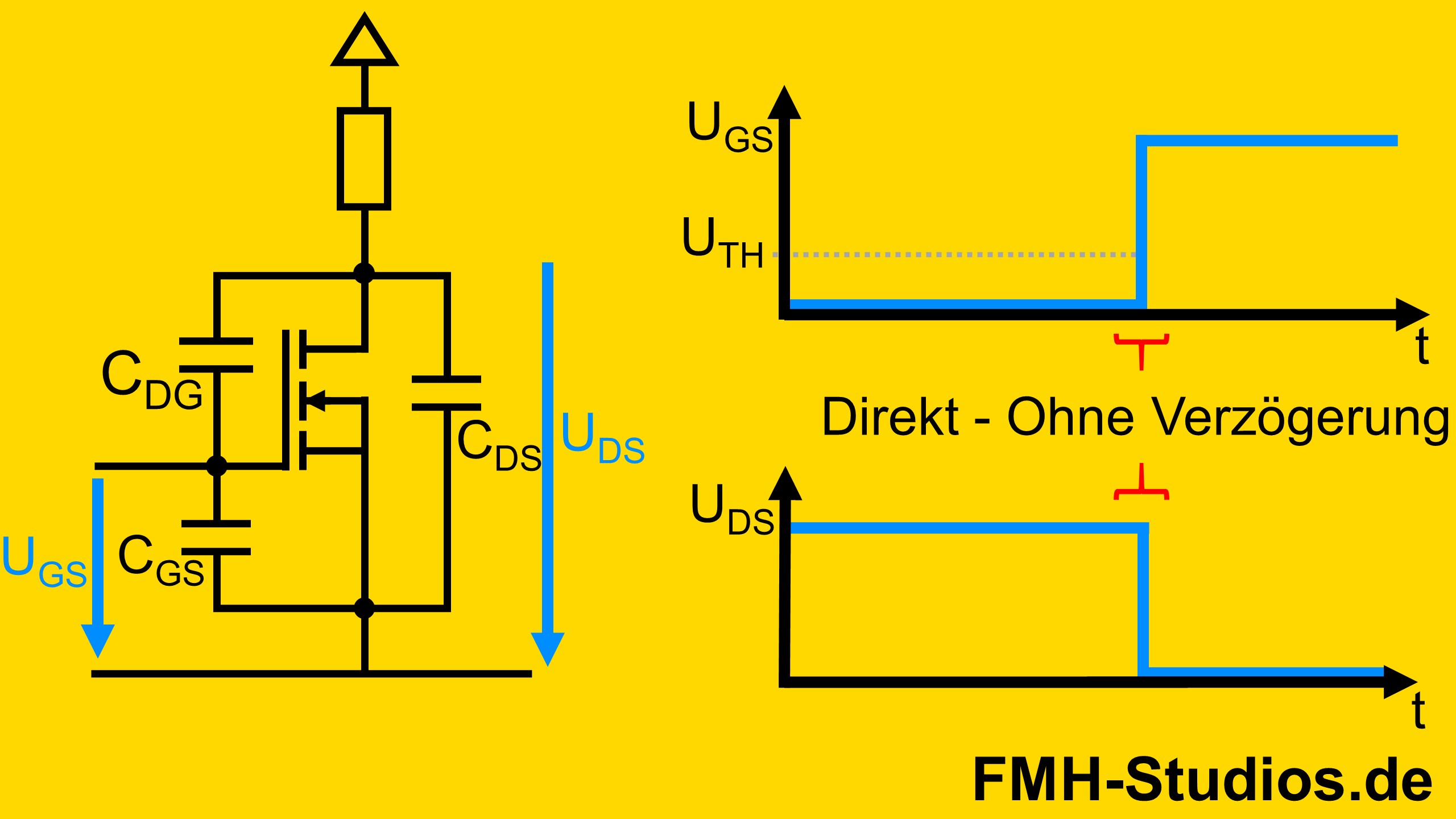

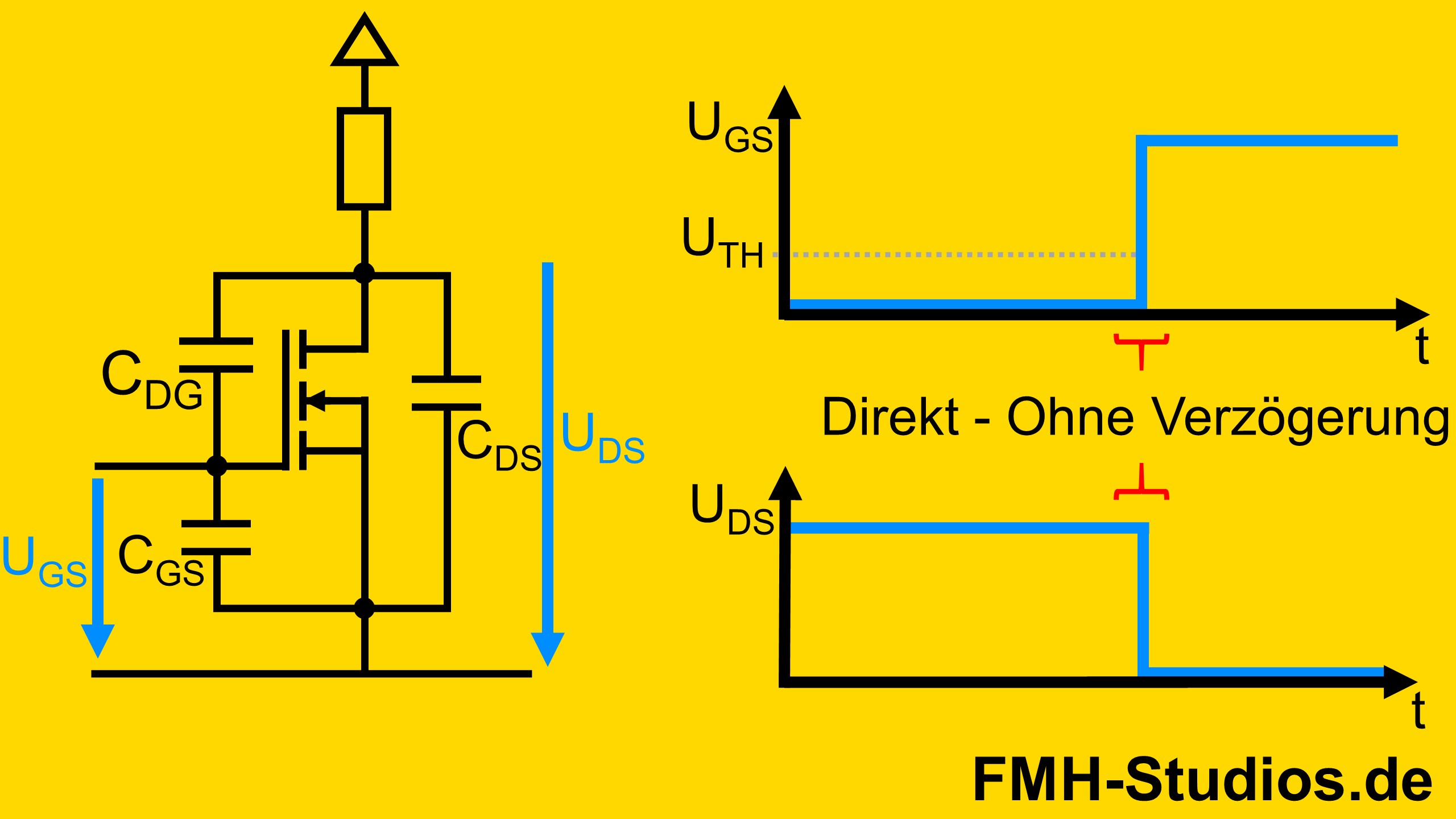

Ideal:

UGS wird schlagartig von 0V auf 5V gehoben. Dies soll dazu führen des UDS ebenfalls schlagartig zur gleichen Zeit auf 0V sinkt.

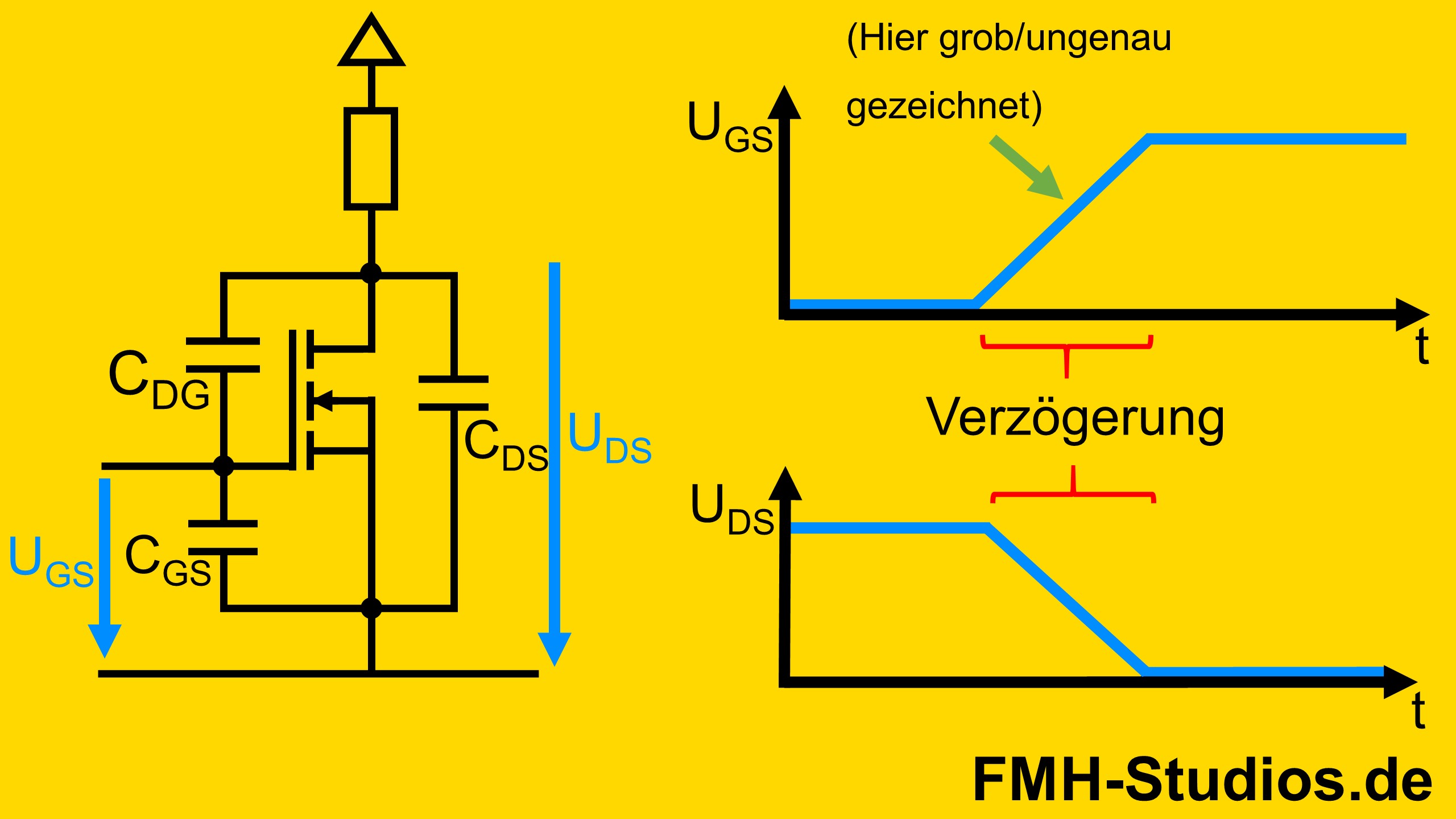

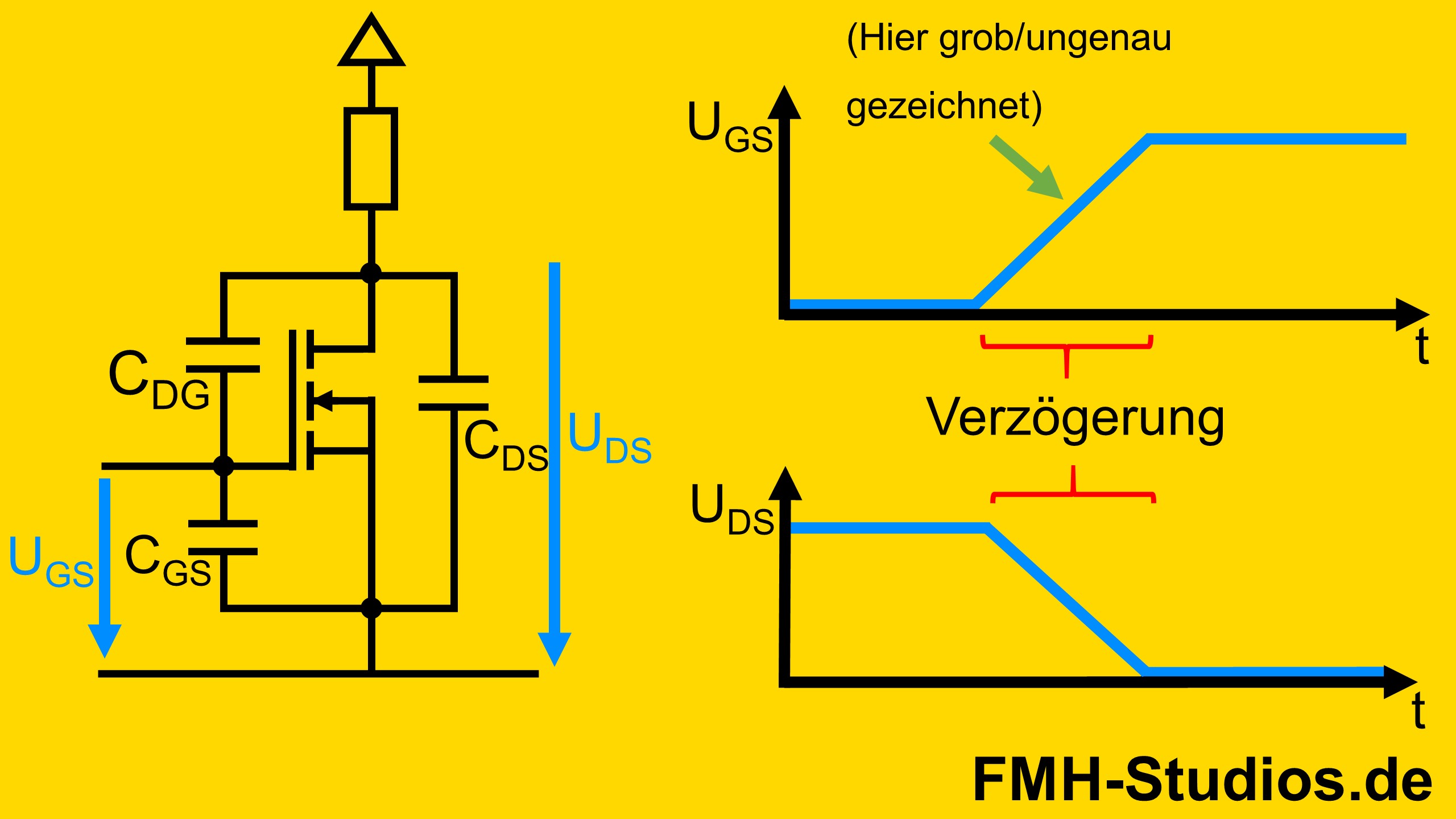

Realität:

In Realität legt man an UGS 5V an. Allerdings benötigt es Zeit bis der Transistor öffnet und UDS auf ~0V absinkt.

Im Folgenden soll erklärt werden warum es zu dieser zeitlichen Verzögerung kommt.

Erklärung des Schaltverhalten

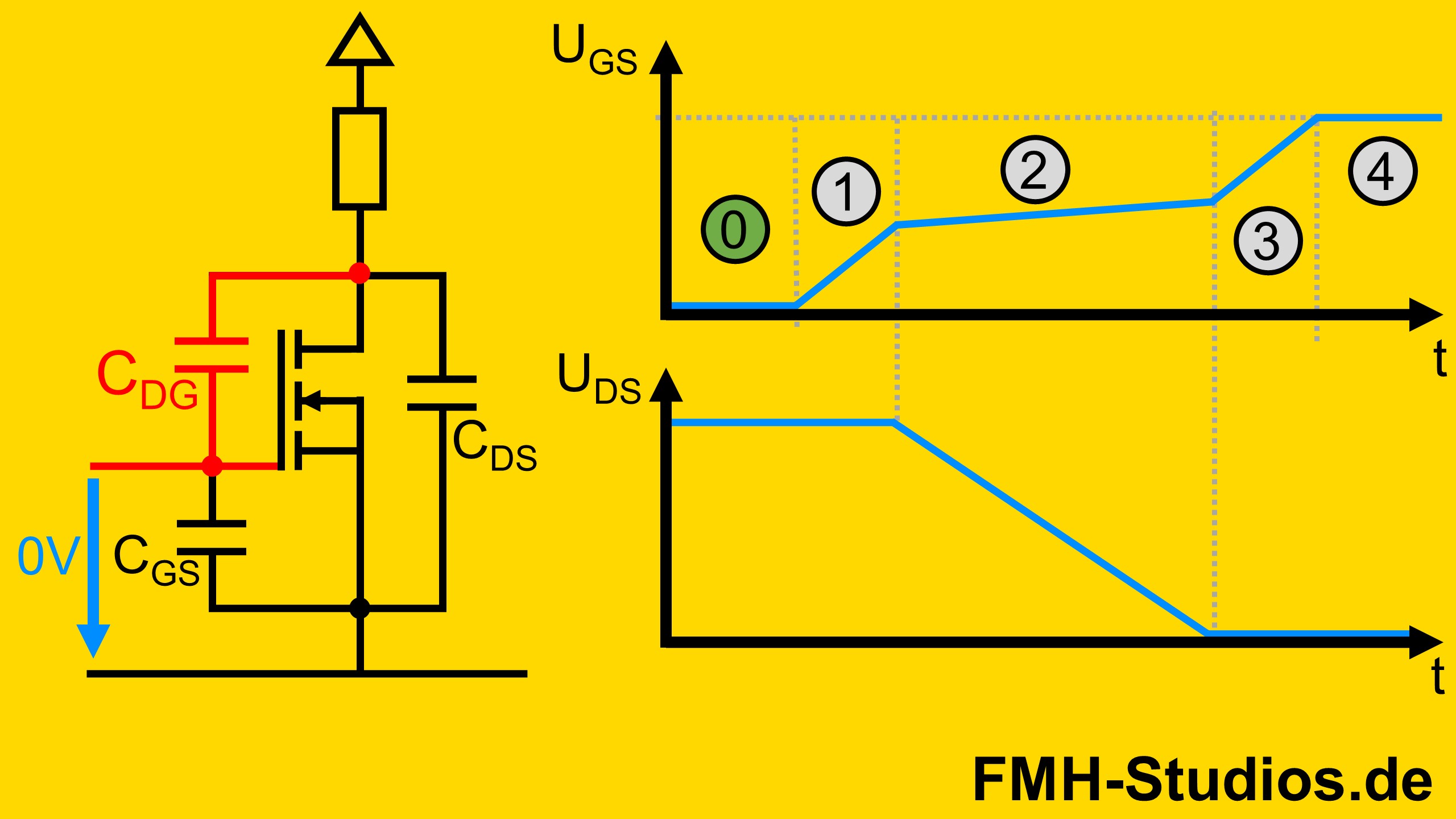

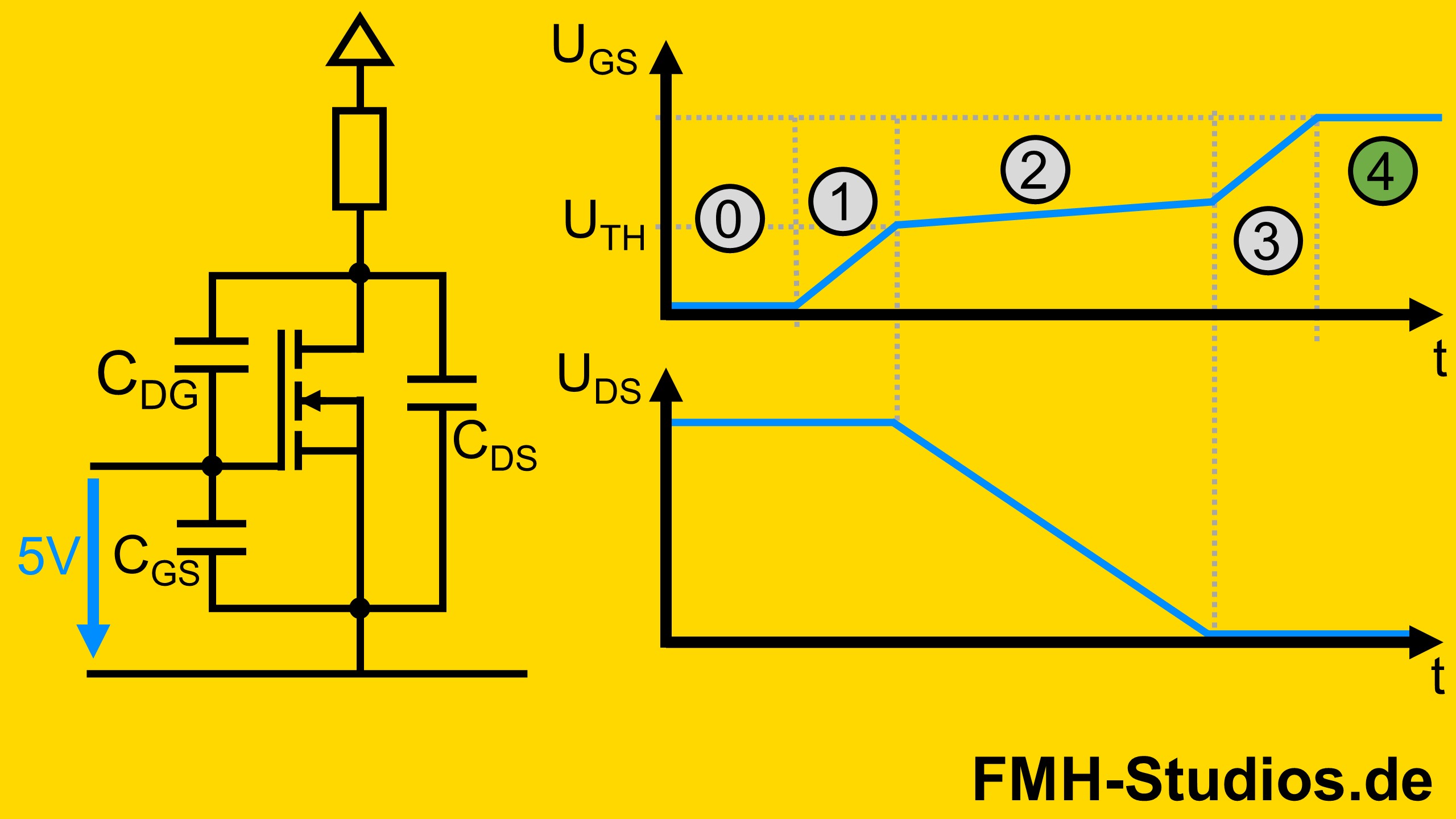

Das Schaltverhalten kann in 4 Bereiche bzw. 4 Phasen unterteilt werden.

Begonnen mit der Phase 0

Phase 0

In der Phase 0 ist der MOSFET noch gesperrt. Das bedeutet über Gate und Source liegt noch keine Spannung an (UGS=0V). VDD beträgt 20V. Da des MOSFET somit noch offen ist, fallen über ihm die vollen 20V ab.

Zunächst betrachtet man die Kapazitäten bzw. die Potentiale:

CDG: Potentiale: D=20V G=0V -> CDG ist geladen

CGS: Potentiale: G=0V S=0V -> CGS ist ungeladen

CDS: Potentiale: D=20V S=0V -> CDS ist geladen

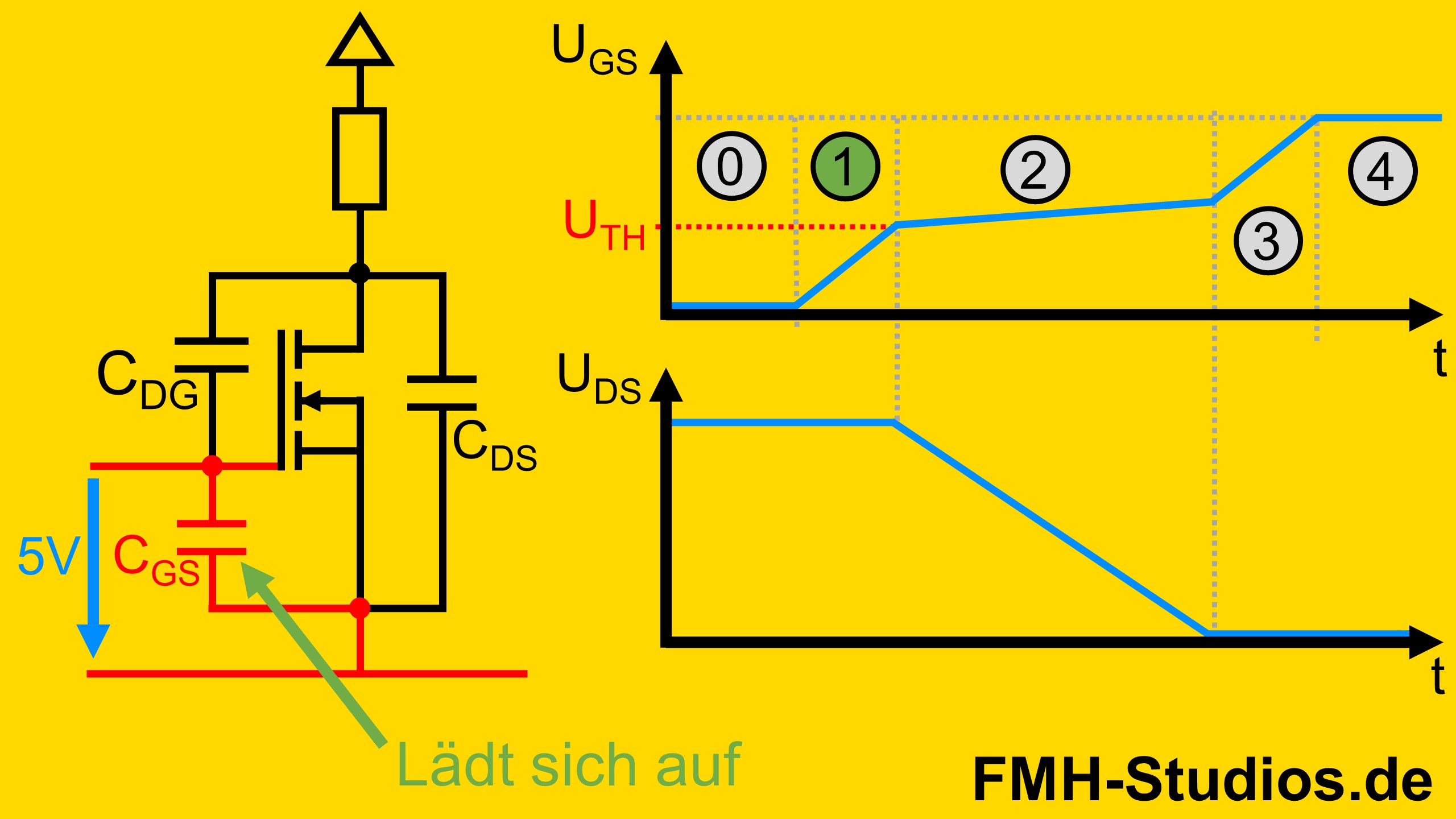

Phase 1

Nun schaltet man UGS auf 5V. Allerdings liegen diese 5V nicht sofort an.

Die Kapazität zwischen Gate und Source (CGS) wird geladen.

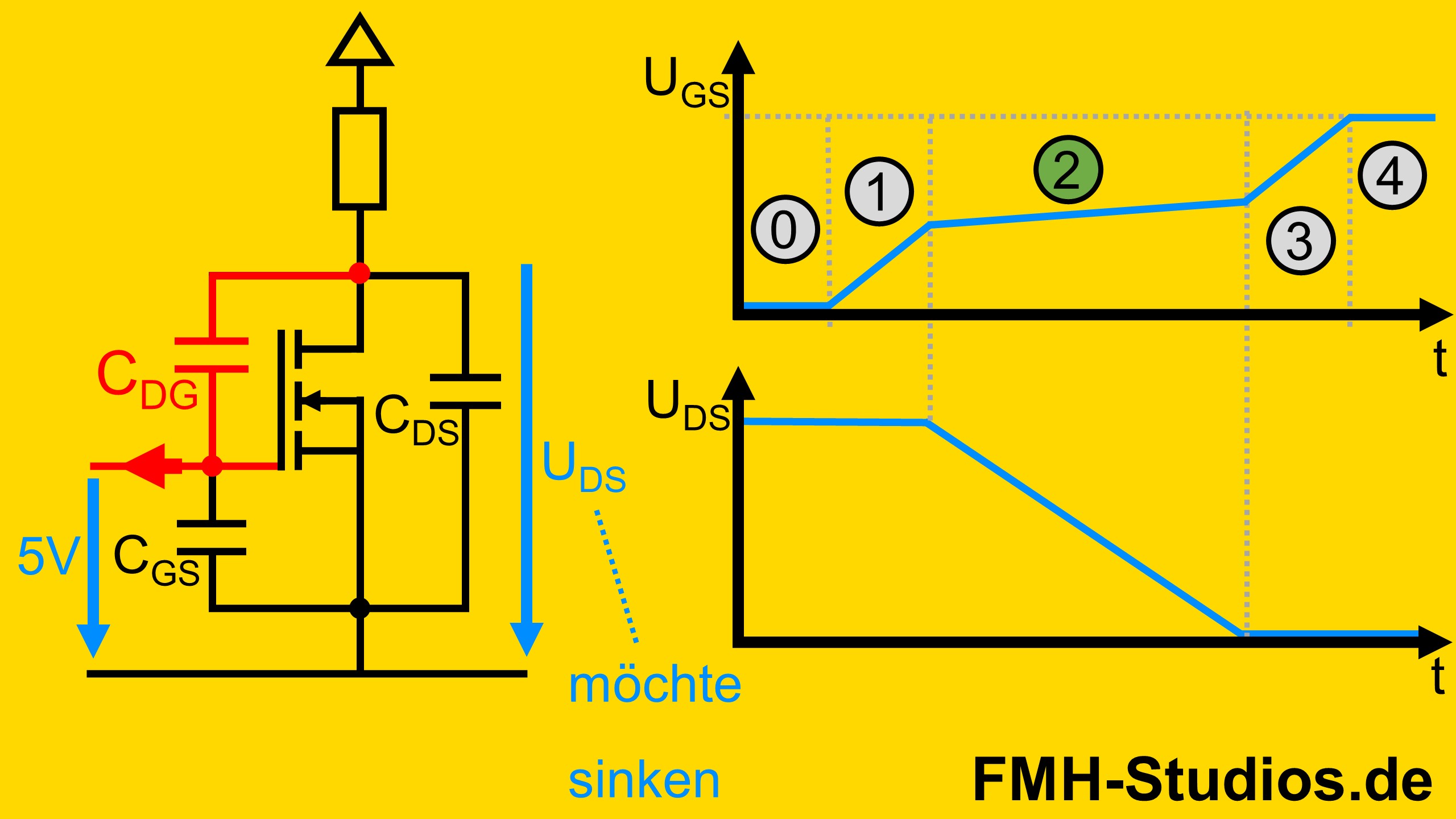

Phase 2

Nun fängt die DS Strecke an durchzusteuern. Das bedeutet das Potential am Drain-Anschluss sinkt. Somit sinkt auch das Potential am CDG, an diesem fällt also weniger Spannung ab. Daher entlädt sich die Kapazität CDG über das Gate.

Das Potential am Drain geht daher auch nur langsam runter, da CDG das Potential immer noch hochhält und dem schnellen Abfall entgegenwirkt.

-> Potential am D möchte schnell runter -> CDG wirkt dem entgegen.

Andersrum wirkt CGD bzw, UDG dem Anstieg von UG entgegen, wodurch sich das Miller-Plateau ergibt.

Zeitlich gesehen bleibt die UGS hierdurch ziemlich konstant.

(Vorsicht bei der Verwendung von Treibern vor dem MOSFET. Diese müssen diesen Strom, welcher in die andere Richtung fließt, aushalten – evtl. Schutzbeschaltung planen

⇨ Treiber )

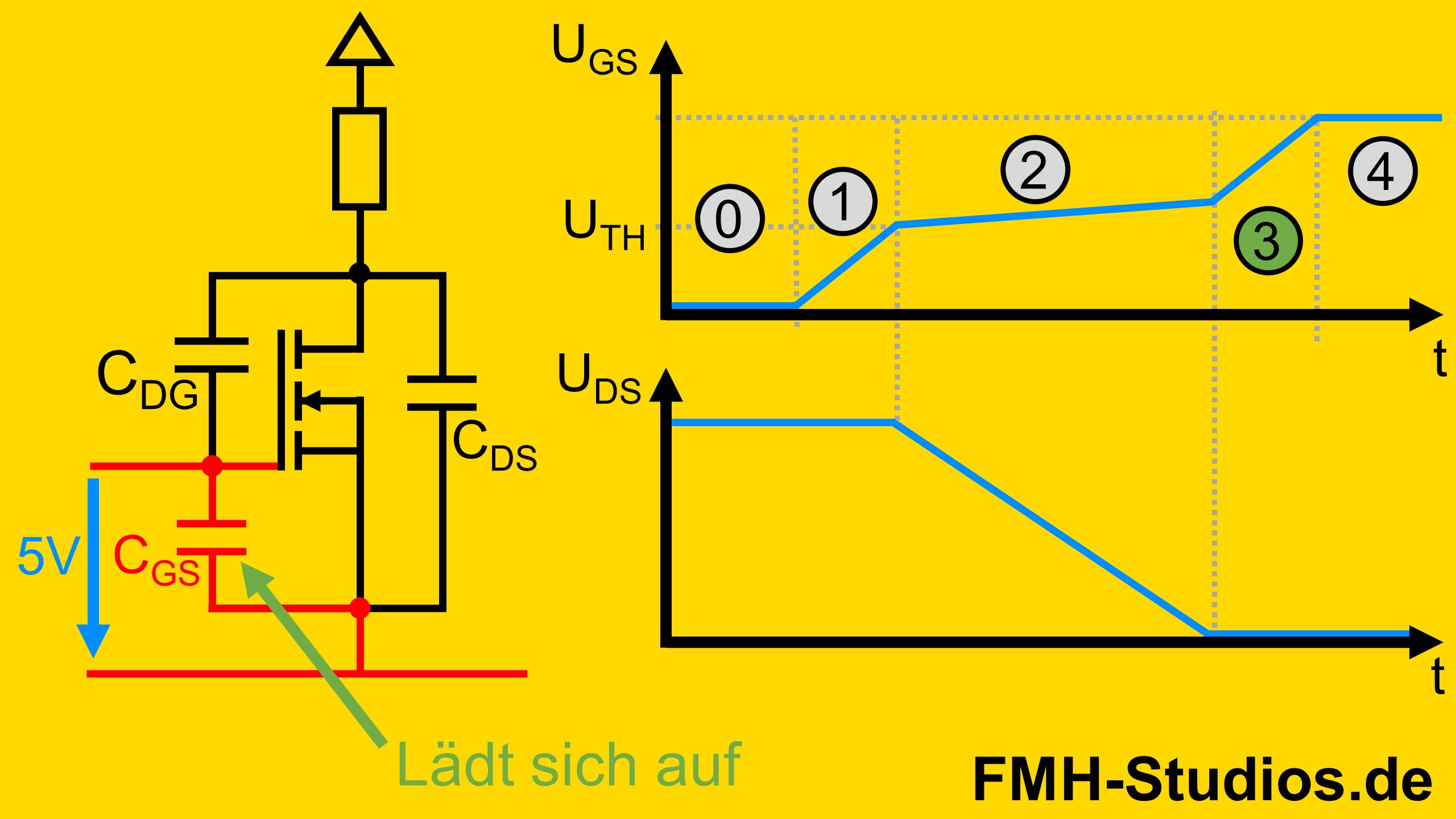

Phase 3

In der letzten Phase wird CGS noch vollständig aufgeladen. Der MOSFET schaltet also vollständig durch.

Ausschaltverhalten

Beim Ausschalten des MOSFET, sprich beim Umschalten von Leitenden in den Sperrenden Zustand, vergeht kommt es ebenfalls zu einer Zeitlichen Verzögerung.

Der Ablauf ist umgekehrt zum Einschaltvorgang.

Die Schaltzeiten sind jedoch nicht dieselben. Die Ausschaltzeit ist immer etwas länger als die Einschaltzeit.

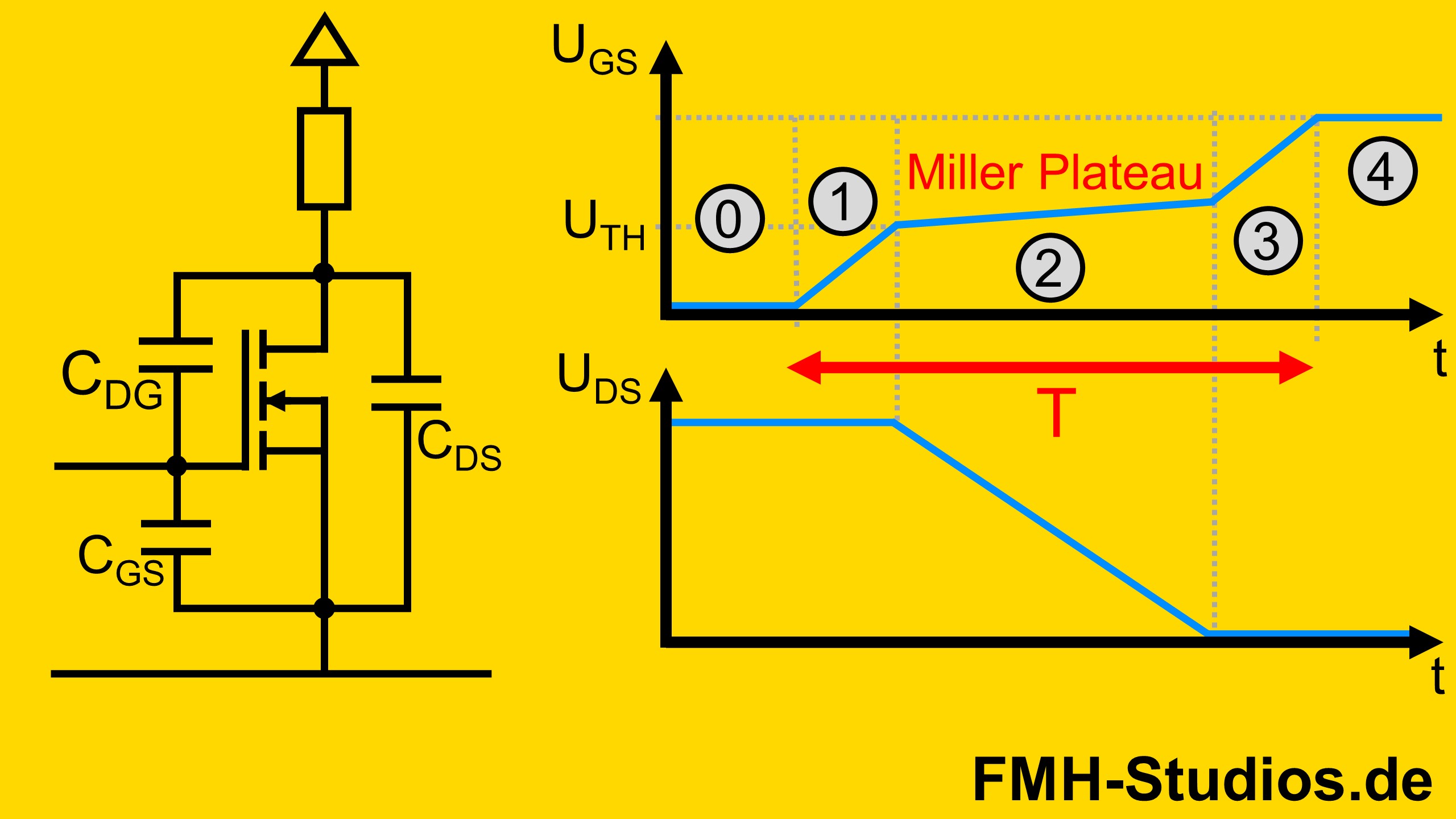

Problem des Miller-Plateau

Idealerweise sollten Phase 1,2,3 keine Zeit aufweisen. Das bedeutet die gewünschte Gate-Source Spannung sollte sofort anliegen und der MOSFET sofort durchschalten.

Wie nun gezeigt ist dies in Realität allerdings nicht so.

Die meiste Zeit beansprucht dabei die Phase 2 – sprich das Miller-Plateau.

Es gilt also diese möglichst kurz zu halten.

Warum?

Diese Verzögerung beim Umschalten des MOSFET führt zu hohen Verlusten. Welche als Schaltverluste bezeichnet werden.

⇨ Verluste des MOSFET

Ein weiteres Problem kann sich beispielsweise bei Halbbrückenschaltungen ergeben. Hierbei werden zwei MOSFETs abwechselnd ein und ausgeschaltet werden. Beide dürfen keinesfalls gleichzeitig an sein.

Aufgrund des MOSFET Schaltverhalten bzw. der Umschaltverzögerung muss hierbei allerdings immer eine Totzeit implementiert werden.

⇨ Halbbrückenschaltung

⇨ Totzeit