Erklärung

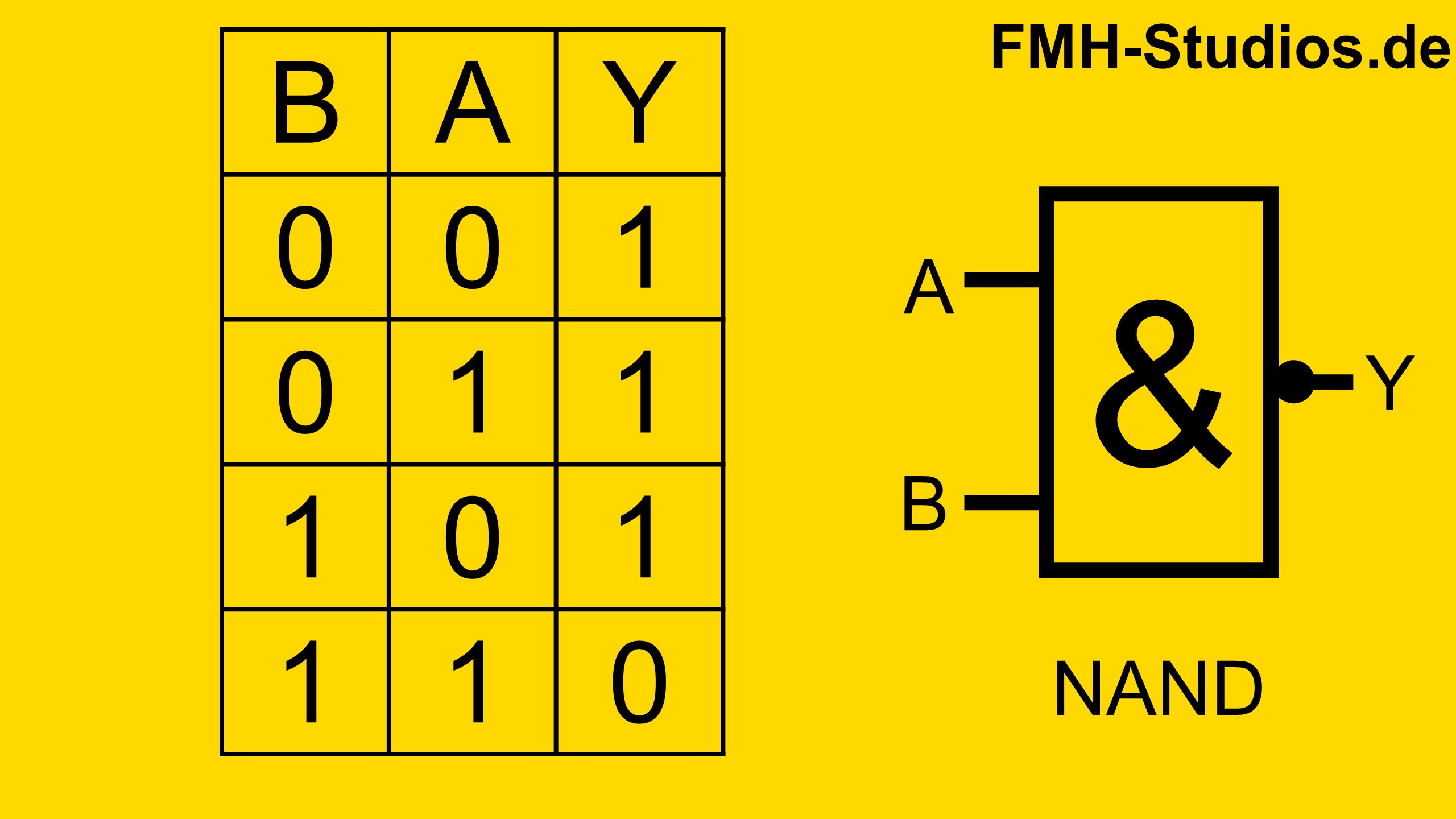

Um das Verhalten dabei besser nachvollziehen zu können, hilft es die Wahrheitstabelle des NAND Gatters durchzugehen.

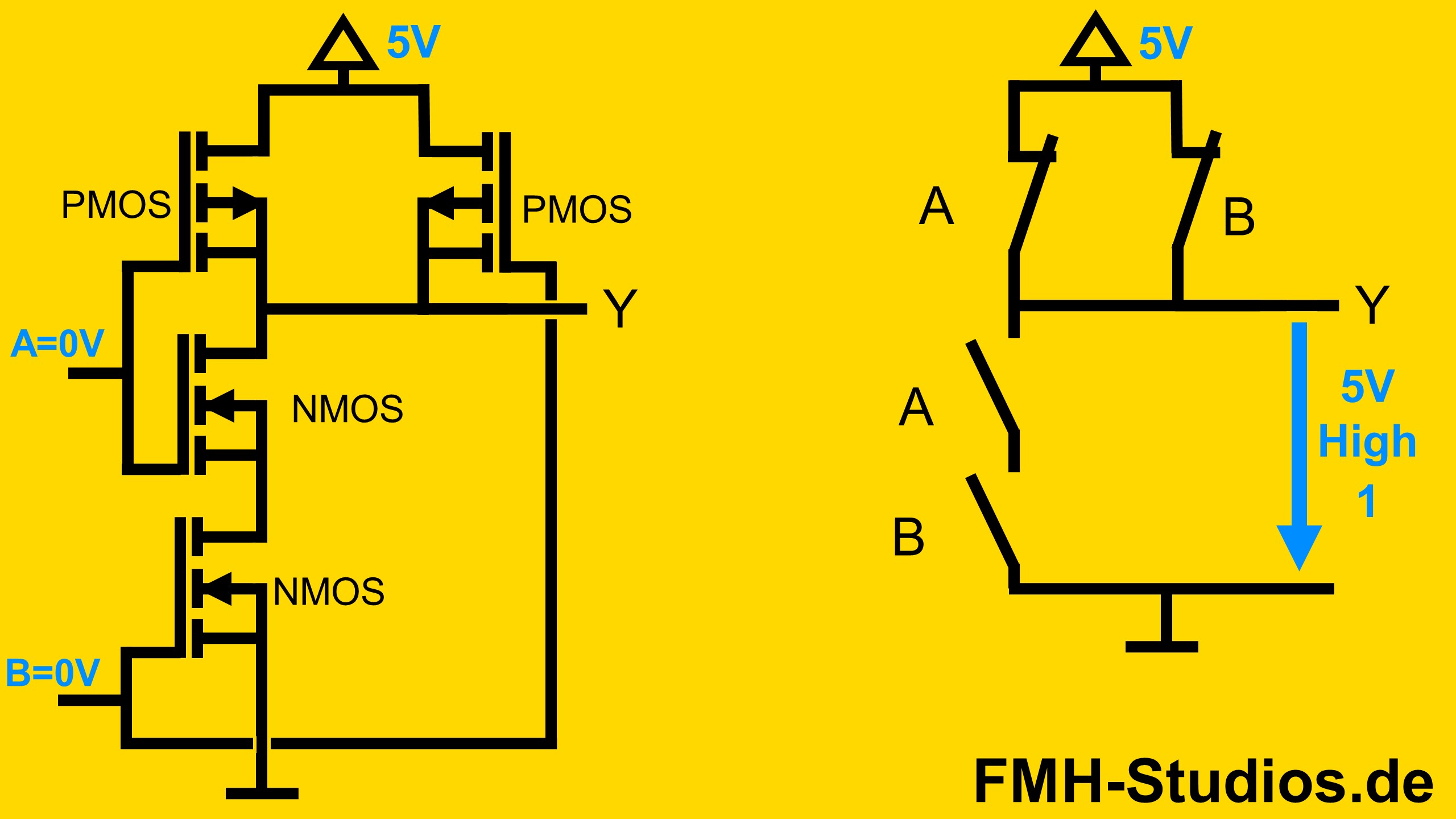

1. Fall: B=0 A=0 -> Y=1

Im ersten Fall wird A und B auf 0 also 0V gesetzt. Hierbei schließen die beiden oberen PMOS die beiden unteren NMOS öffnen.

Die vollen 5V fallen so über den beiden unteren NMOS ab, da diese wie 2 offene Schalter wirken. Die beiden oberen PMOS wirken wie geschlossene Schalter.

Am Ausgang fällt entsprechend 5V ab. Also der High-Pegel was entsprechend für eine 1 steht.

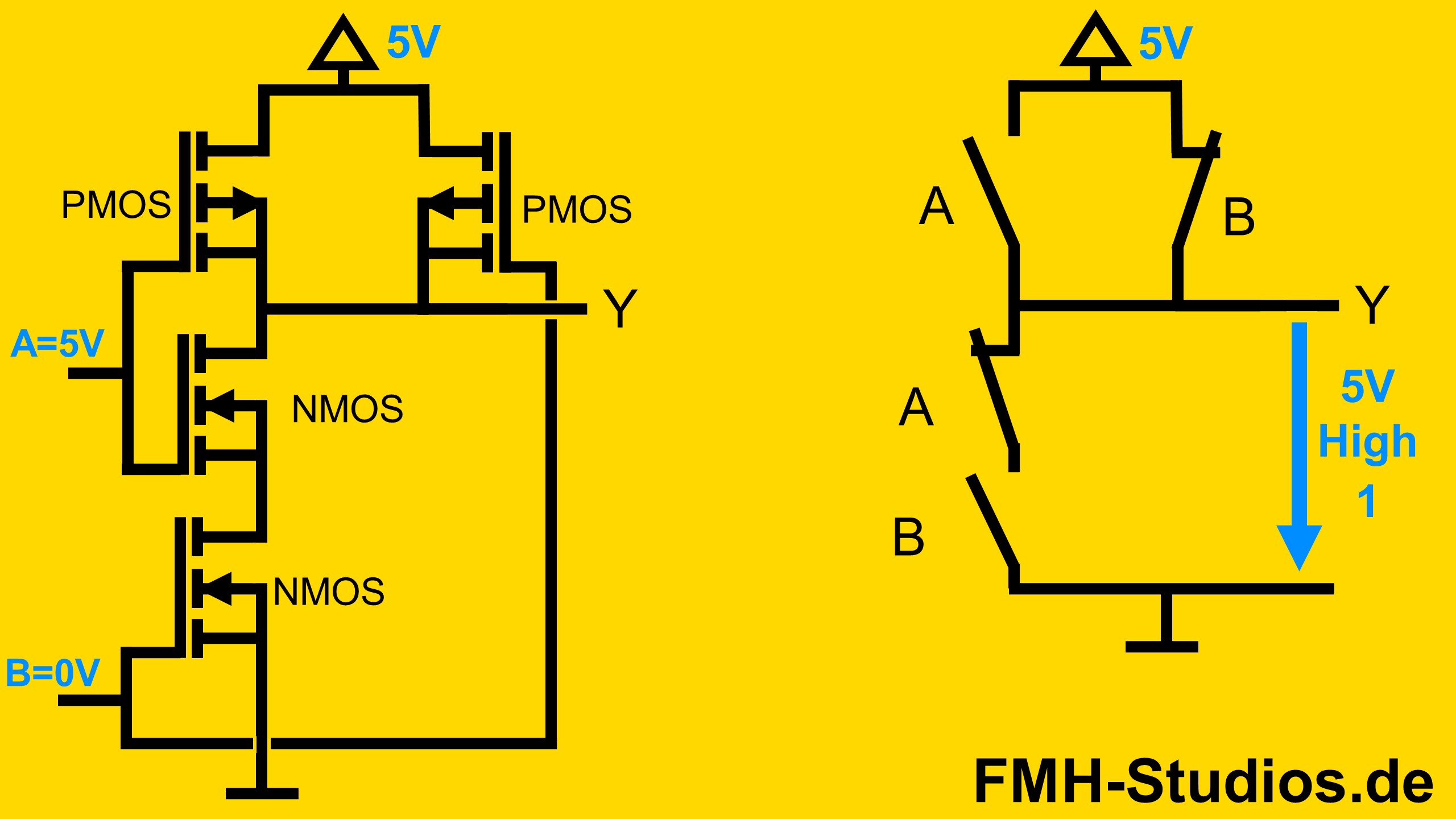

2. Fall: B=0 A=1 -> Y=1

Im zweiten Fall wird B auf 0 also 0V und A auf 1 also 5V gesetzt. Bei den beiden oberen PMOS öffnet der linke (A) und der rechte PMOS schließt (B).

Von den beiden unteren NMOS schließt A und der B öffnet.

Die vollen 5V fallen so über beim unteren B NMOS ab.

Am Ausgang fällt entsprechend 5V ab. Also der High-Pegel was entsprechend für eine 1 steht.

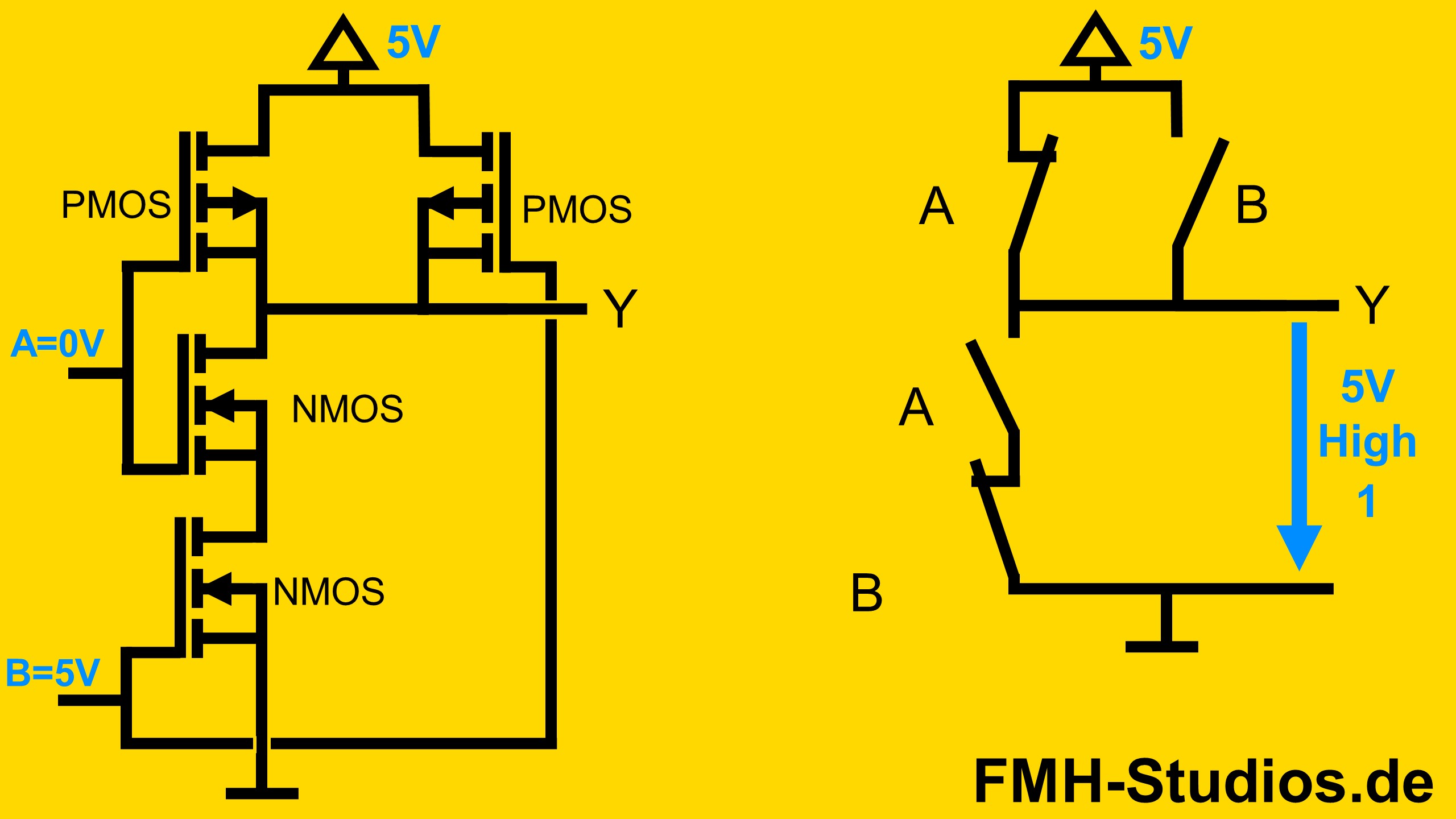

3. Fall: B=1 A=0 -> Y=1

Im dritten Fall wird B auf 1 also 5V und A auf 0 also 0V gesetzt. Bei den beiden oberen PMOS öffnet der rechte (B) und der linke PMOS schließt (A).

Von den beiden unteren NMOS schließt B und der A öffnet.

Die vollen 5V fallen so über beim unteren A NMOS ab.

Am Ausgang fällt entsprechend 5V ab. Also der High-Pegel was entsprechend für eine 1 steht.

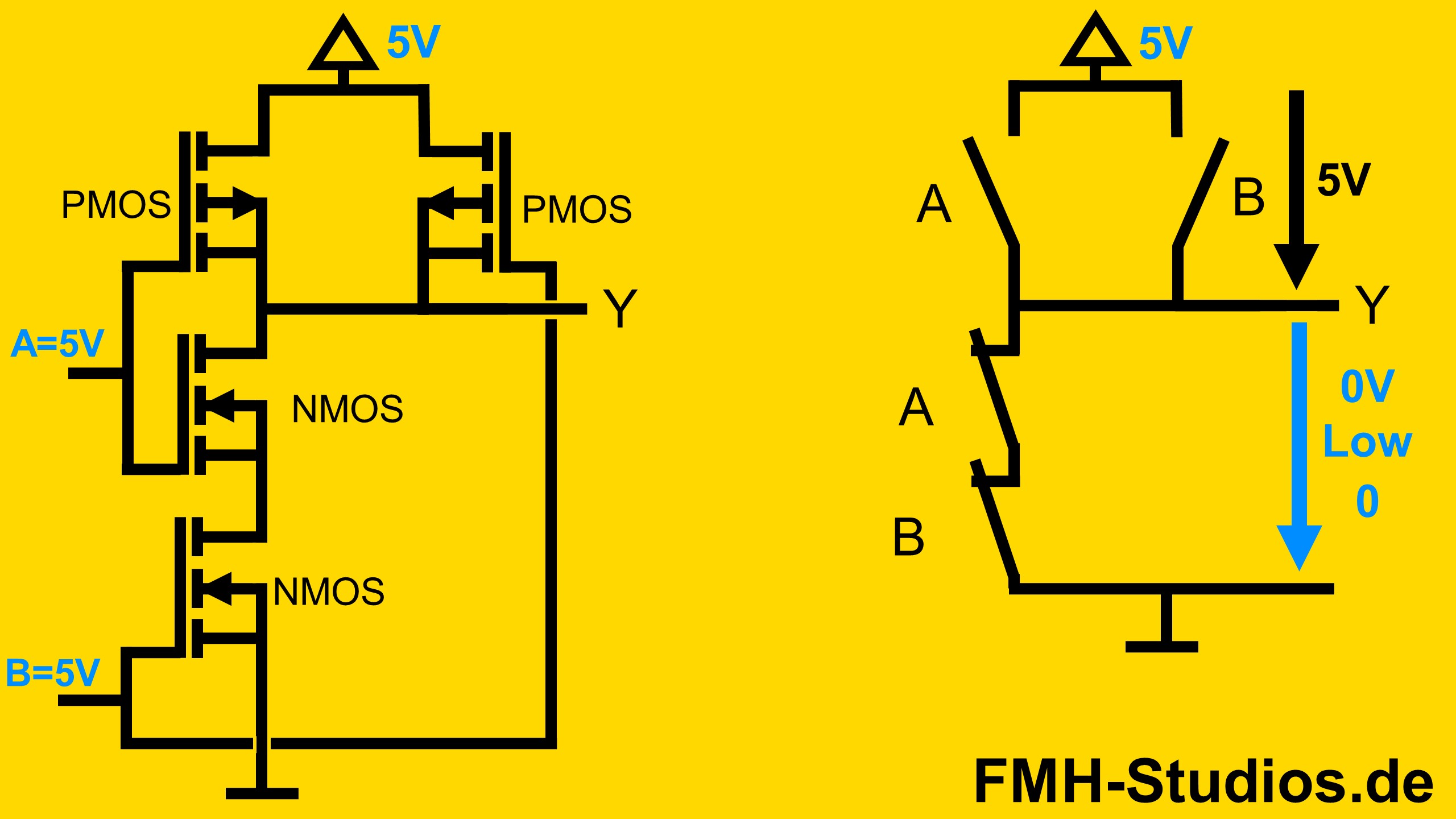

4. Fall: B=1 A=1 -> Y=0

Im vierten Fall wird A und B auf 1 also 5V gesetzt. Hierbei öffnen die beiden oberen PMOS die beiden unteren NMOS schließen.

Die vollen 5V fallen so über den beiden oberen PMOS ab, da diese wie 2 offene Schalter wirken. Die beiden unteren NMOS wirken wie geschlossene Schalter. Über ihnen fällt entsprechend 0V ab.

Am Ausgang fällt entsprechend 0V ab. Also der Low-Pegel was entsprechend für eine 0 steht.